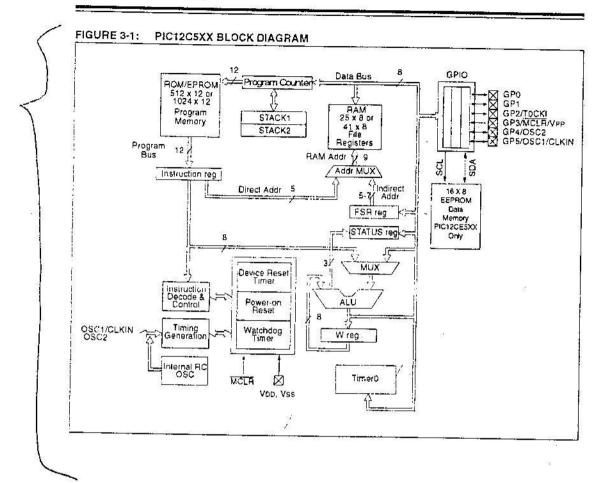

## PIC12C5XX

## The MPC603 block diagram

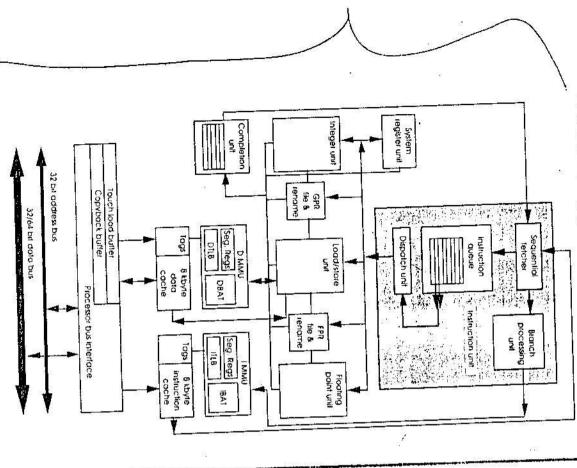

appear. Like the MPC601, it has the three execution units: a aranch unit to resolve branch instructions, an integer unit and The MPC603 was the second PowerPC processor to

floating point unit.

ever, two additional execution units have been added to provide dedicated support for system registers and to move data between the register files and the two onchip caches. The tion and process five every clock cycle. processor is superscalar and can dispatch up to three instruc-The floating point unit supports IEEE format. How-

speculative execution. It augments this with register renamadvantages of the processor. than allowed on the MPC601 and thus increase the processing ing, which allows speculative execution to continue further The branch unit supports both branch folding and

a 32 bit address linear organisation and is 4 Gbytes in size. precision floating point. The external physical memory map is contains 32 registers, each 64 bits wide to support double registers, each 32 bits wide. The floating point register file The general purpose register file consists of 32 separate

bit address bus and a 64 or 32 bit data bus. This bus can, at its rate memory management unit and on chip cache for data and ing is also provided to ensure cache coherency with external ously with the data bus to improve its utilisation. Bus snoopof 16 Kbyles. The bus also supports split transactions, where cache is 8 Kbytes in size, giving a combined on chip cache size peak, feich two instruction per clock or 64 bits of data. Each instructions which communicates to external memory via a 32 memory. the address bus can be used independently and simultanehe MPC603's memory subsystem consists of a sepa-

instruction fetches. It is different from the MPC601 in that divided into two pairs, one for data accesses and the other for in one of four translation lookaside buffers, each of which is dress translation process, by keeping translation information automatically by the processor. translation tablewalks are performed in software and not As with the MPC601, the MPC603 speeds up the ad-

and is eminently suitable for low power applications. The device also includes power management facilities

diadram

100

MPC603 internal block

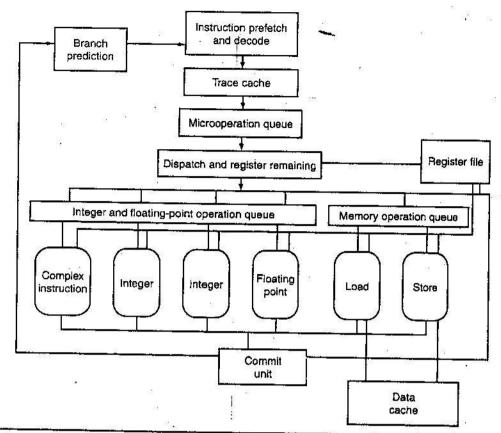

FIGURE 8.80 The microerchitecture of the Intel Pentium 4. The extensive queues allow up to 126 microoperations to be outstanding at any point in time, including 48 loads and 24 stores. There are actually seven functional units, since the FP unit includes a separate dedicated unit for floating-point moves. The load and store units are actually separated into two parts, with the first part handling address calculation and the second part responsible for the actual memory reference. The integer ALUs operate at twice the clock frequency, allowing two integer ALU operations to be completed by each of the two integer units in a single clock cycle. As we described in Chapter 5, the Pentium 4 uses a special cache, called the trace cache, to hold predecoded sequences of microoperations, corresponding to IA-32 instructions. The operation of a trace cache is explained in more detail in Chapter 7. The FP unit also handles the MMX multimedia and SSE2 instructions. There is an extensive bypass network among the functional units; since the pipeline is dynamic rather than static, bypassing is done by tagging results and tracking source operands, so as to allow a match when a result is produced for an instruction in one of the queues that needs the result. Intel is expected to release new versions of the Pentium 4 in 2004, which will probably have changes in the microarchitecture.

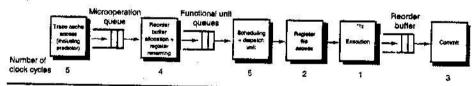

FIGURE 6.51 The Pentium 4 pipeline showing the pipeline flow for a typical instruction and the number of clock cycles for the major steps in the pipeline. The major buffers where instructions wait are also shown.